## IMPLEMENTATION AND SIMULATION OF MC68HC11 MICROCONTROLLER UNIT USING SYSTEMC FOR CO-DESIGN STUDIES

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

ΒY

CUMHUR ERKAN TUNCALI

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN THE DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2007

### Approval of the Thesis

## IMPLEMENTATION AND SIMULATION OF MC68HC11 MICROCONTROLLER UNIT USING SYSTEMC FOR CO-DESIGN STUDIES

Submitted by **CUMHUR ERKAN TUNCALI** in partial fulfillment of the requirements for the degree of **Master of Science in Electrical and Electronics Engineering** by,

| Prof. Dr. Canan Özgen Dean, Graduate School of <b>Natural and Applied Sciences</b>         |

|--------------------------------------------------------------------------------------------|

| Prof. Dr. İsmet Erkmen<br>Head of Department, <b>Electrical and Electronics Eng., METU</b> |

| Prof. Dr. Murat Aşkar<br>Supervisor, Electrical and Electronics Engineering, METU          |

| Examining Committee Members:                                                               |

| Prof. Dr. Hasan Güran (*)<br>Electrical and Electronics Engineering, METU                  |

| Prof. Dr. Murat Aşkar (**)<br>Electrical and Electronics Engineering, METU                 |

| Assist. Prof. Dr. Cüneyt Bazlamaçcı<br>Electrical and Electronics Engineering, METU        |

| Assoc. Prof. Dr. Gözde Bozdağı Akar<br>Electrical and Electronics Engineering, METU        |

| M.Sc. Lokman KESEN<br>ASELSAN                                                              |

| Date:                                                                                      |

| (*) Head of Examining Committee                                                            |

(\*\*) Supervisor

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Cumhur Erkan Tuncalı

:

Signature

## ABSTRACT

## IMPLEMENTATION AND SIMULATION OF MC68HC11 MICROCONTROLLER UNIT USING SYSTEMC FOR CO-DESIGN STUDIES

Tuncalı, Cumhur Erkan

M.Sc., Department of Electrical and Electronics Engineering

Supervisor: Prof. Dr. Murat Aşkar

December 2007, 127 pages

In this thesis, co-design and co-verification of a microcontroller hardware and software using SystemC is studied. For this purpose, an MC68HC11 microcontroller unit, a test bench that contains input and output modules for the verification of microcontroller unit are implemented using SystemC programming language and a visual simulation program is developed using C# programming language in Microsoft .NET platform.

SystemC is a C++ class library that is used for co-designing hardware and software of a system. One of the advantages of using SystemC in system design

is the ability to design each module of the system in different abstraction levels. In this thesis, test bench modules are designed in a high abstraction level and microcontroller hardware modules are designed in a lower abstraction level.

At the end, a simulation platform that is used for co-simulation and co-verification of hardware and software modules of overall system is developed by combining microcontroller implementation, test bench modules, test software and visual simulation program. Simulations at different levels are performed on the system in the developed simulation platform. Simulation results helped observing errors in designed modules easily and making corrections until all results verified designed hardware modules. This stuation showed that co-designing and co-verifying hardware and software of a system helps finding errors and making corrections in early stages of system design cycle and so reducing design time of the system.

Keywords: SystemC, MC68HC11, Microcontroller Simulator, Hardware and Software Co-design, SystemC Visual Simulation Tool.

## BÜTÜNLEŞİK TASARIM ÇALIŞMALARI İÇİN MC68HC11 MİKRODENETLEYİCİSİNİN SYSTEMC KULLANILARAK GERÇEKLEŞTİRİLMESİ VE SİMÜLASYONUNUN YAPILMASI

Tuncalı, Cumhur Erkan

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü

Tez Yöneticisi: Prof. Dr. Murat Aşkar

Aralık 2007, 127 sayfa

Bu tezde, bir mikrodenetleyicinin donanım ve yazılımının SystemC kullanılarak bütünleşik tasarım ve bütünleşik doğrulaması incelenmiştir. Bu amaçla, SystemC programlama dili kullanılarak, bir MC68HC11 mikrodenetleyici ünitesi, mikrodenetleyici ünitesini doğrulamak için giriş ve çıkış modülleri içeren bir test ünitesi ve Microsoft .NET platformunda C# programlama dili kullanılarak bir görsel simülasyon programı geliştirilmiştir.

SystemC, bir sistemin donanım ve yazılımının bütünleşik tasarımının yapılması için kullanılan bir C++ sınıf kütüphanesidir. Sistem tasarımlarında SystemC

kullanımının avantajlarından birisi, sistemin her modülünü farklı soyutlama seviyelerinde tasarlama imkanıdır. Bu tezde, test modülleri yüksek bir soyutlama seviyesinde, mikrodenetleyici donanımı modülleri ise daha düşük bir soyutlama seviyesinde tasarlanmıştır.

Neticede, gerçekleştirilmiş mikrodenetleyici, test modülleri, test yazılımı ve görsel simülasyon program birleştirilerek, bütün sistemin donanım ve yazılım modüllerinin bütünleşik simülasyon ve bütünleşik doğrulamasını yapmak için kullanılan bir simülasyon platformu oluşturulmuştur. Geliştirilen simülasyon platformunda, sistem üzerinde farklı seviyelerde simülasyonlar uygulanmıştır. Simülasyon sonuçları, tüm sonuçlar tasarlanan donanım modüllerini doğrulayana dek tasarlanan modüllerdeki hataları kolaylıkla görmeye ve düzeltmelerin yapılmasına yardımcı olmuştur. Bu durum, bir sistemin donanım ve yazılımının bütünleşik tasarım ve bütünleşik doğrulamasının, sistem tasarım sürecinin erken safhalarında hataları bulmaya, düzeltmelerin yapılmasına ve böylece sistem tasarım süresinin düşmesine yardımcı olduğunu göstermiştir.

Anahtar Kelimeler: SystemC, MC68HC11, Mikrodenetleyici Simülatörü, Donanım ve Yazılım Bütünleşik Tasarımı, SystemC Görsel Simülasyon Aracı

To My Family

## ACKNOWLEDGEMENTS

The author would like to express his deepest gratitude to Prof. Dr. Murat Aşkar for his guidance, encouragement and unlimited patience throughout this thesis work.

The author would also like to thank his colleagues in BOTT for their encouragement and support.

Finally, the author would like to express his special thanks to his family for their great support during this thesis work.

# TABLE OF CONTENTS

| ABSTRACT              | iv   |

|-----------------------|------|

| ÖZ                    | vi   |

| ACKNOWLEDGEMENTS      | ix   |

| TABLE OF CONTENTS     | x    |

| LIST OF FIGURES       | xii  |

| LIST OF TABLES        | xvi  |

| LIST OF ABBREVIATIONS | xvii |

### CHAPTER

| 1. INTRO | DUCTION                                            | 1  |

|----------|----------------------------------------------------|----|

|          | SYSTEMC FOR HARDWARE / SOFTWARE_CO-DESIGN ANI      |    |

| 2.1      | Need for Hardware / Software Co-design of Systems  | 7  |

| 2.2      | Using SystemC for Co-design                        | 8  |

| 2.3      | Development Environment for SystemC                | 11 |

| 3. M68HC | 11 FAMILY OF MICROCONTROLLER UNITS                 | 16 |

| 3.1      | General Description                                | 16 |

| 3.2      | Operation Modes of MC68HC11                        | 19 |

| 3.3      | On-Chip Memory Systems                             | 20 |

| 3.4      | Central Processing Unit (CPU)                      | 22 |

| 3.5      | Addressing Modes                                   | 25 |

| 3.6      | Parallel Input / Output (I/O)                      | 26 |

| 3.7      | Synchronous Serial Peripheral Interface (SPI)      | 31 |

| 3.8      | Asynchronous Serial Communications Interface (SCI) | 33 |

| 3.9      | Main Timer and Real Time Interrupt                 | 35 |

| 3.10     | Pulse Accumulator                                  | 36 |

| USIN      | IG SYSTEMC                                      | 37  |

|-----------|-------------------------------------------------|-----|

| 4.1       | MC68HC11 SystemC Model Internal Structure       | 38  |

| 4.2       | CPU Controller Unit                             | 40  |

| 4.3       | Clock Divider                                   | 45  |

| 4.4       | Arithmetic and Logic Unit (ALU)                 | 47  |

| 4.5       | Register File                                   | 56  |

| 4.6       | Address Bus Controller                          | 60  |

| 4.7       | Handshake I/O Module                            | 63  |

| 4.8       | Timer System                                    | 64  |

| 4.9       | Serial Communications Module                    | 67  |

| 4.10      | Read Only Memory (ROM)                          | 69  |

| 4.11      | Random Access Memory (RAM)                      | 71  |

| 4.12      | Electrically Erasable Programmable ROM (EEPROM) | 73  |

| 4.13      | VLSI Implementation of SystemC Modules          | 75  |

| 5. VISUAL | SIMULATION PLATFORM                             | 77  |

| 5.1       | Structure of Visual Simulation Platform         | 77  |

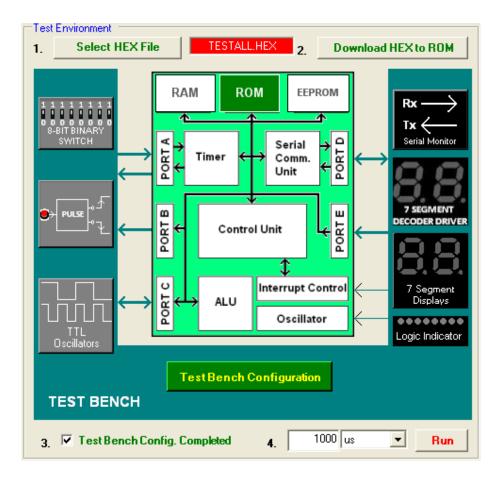

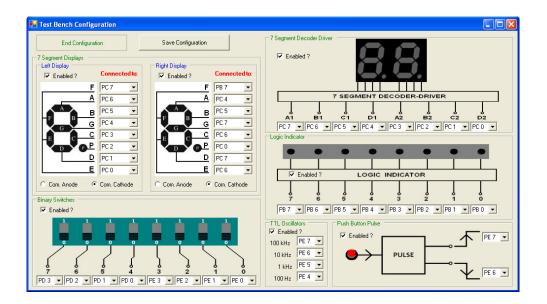

| 5.2       | Test Bench                                      | 78  |

| 5.3       | Features of Visual Simulation Software          | 79  |

| 6. CONCL  | USIONS                                          | 94  |

| REFERENC  | ES                                              | 98  |

| APPENDIX  |                                                 |     |

| A. M68HC  | 11 INSTRUCTION SET                              | 100 |

| B. MICRO  | CONTROLLER TEST CODE                            | 109 |

| B.1       | Instructions and Addressing Modes Test Program  | 109 |

| B.2       | Execution of Test Program on Original MC68HC11  | 115 |

| B.2. S    | erial Port Test Program                         | 119 |

| C. VISUAI | _ SIMULATION TOOL USER GUIDE                    | 120 |

#### 4. DESIGN OF MC68HC11 MICROCONTROLLER MODEL

# LIST OF FIGURES

| Figure 2.1: | A Typical Example of SoC Systems.                  | 7  |

|-------------|----------------------------------------------------|----|

| Figure 2.2: | Design Flow Comparison                             | 10 |

| Figure 2.3: | "Open Workspace" Menu Item in Microsoft Visual C++ | 12 |

| Figure 2.4: | Building SystemC Library                           | 12 |

| Figure 2.5: | Enabling Run-Time Type Information                 | 13 |

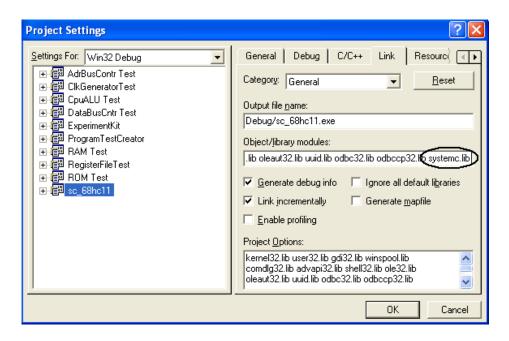

| Figure 2.6: | Including SystemC Library to Library List          | 14 |

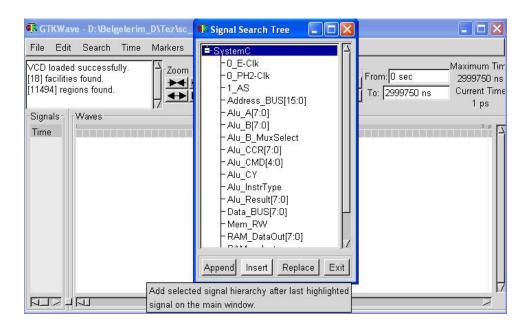

| Figure 2.7: | Inserting Signals in GTKWave                       | 15 |

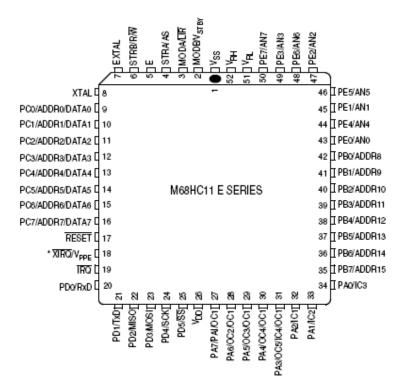

| Figure 3.1: | MC68HC11E9 Pin Assignments                         | 17 |

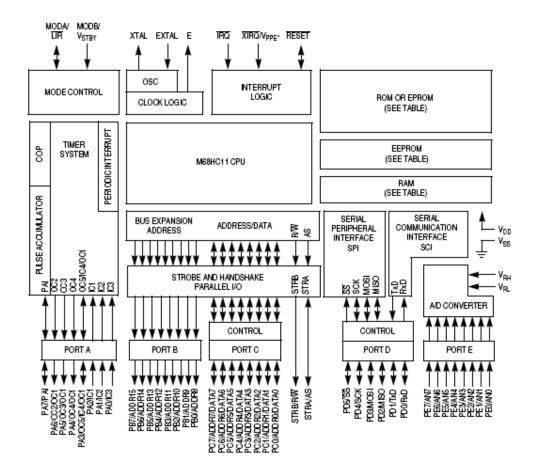

| Figure 3.2: | Block Diagram of MC68HC11E9                        | 18 |

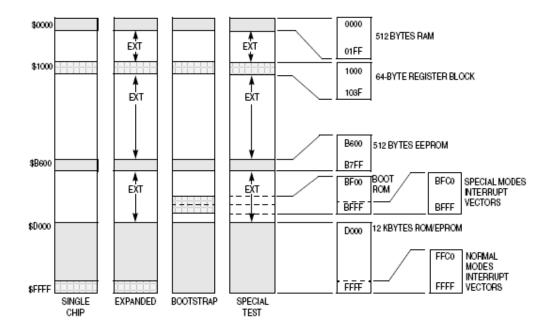

| Figure 3.3: | Memory Map of MC68HC11E9                           | 20 |

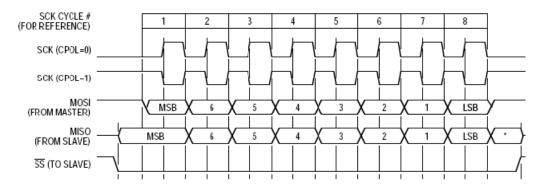

| Figure 3.4: | CPHA Equals Zero SPI Transfer Format               | 32 |

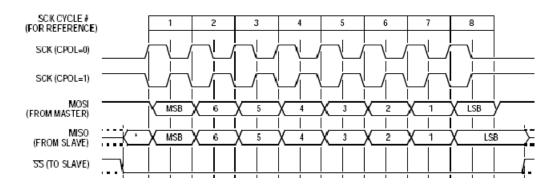

| Figure 3.5: | CPHA Equals One SPI Transfer Format                | 33 |

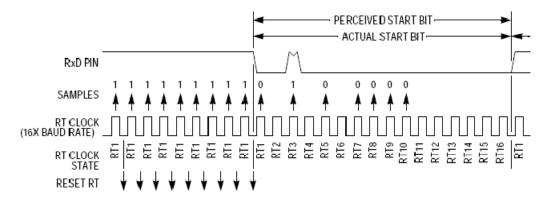

| Figure 3.6: | Start Bit Reception                                | 34 |

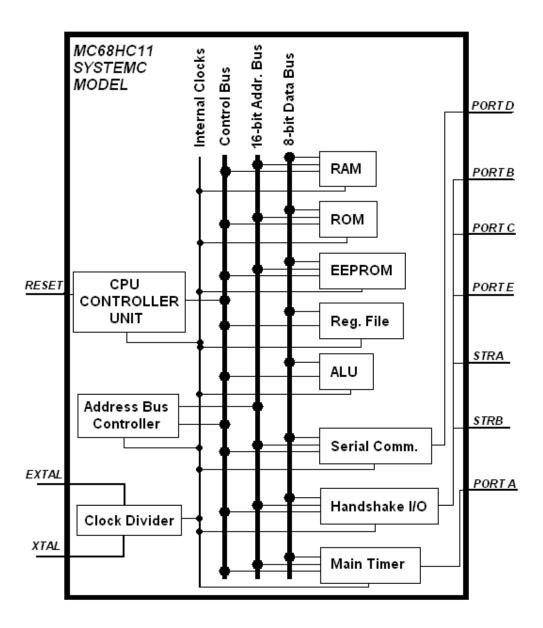

| Figure 4.1: | Internal Structure of MC68HC11 SystemC Model       | 39 |

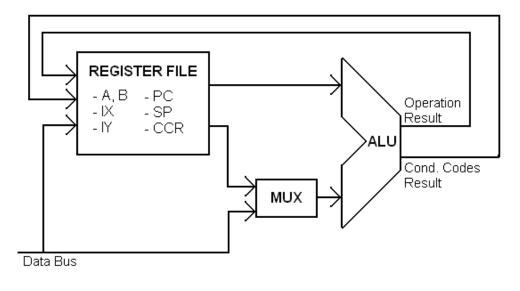

| Figure 4.2: | Datapath of Microprocessor                         | 40 |

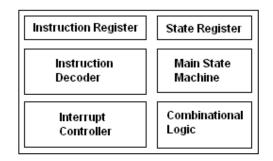

| Figure 4.3: | Block Diagram of CPU Controller                    | 41 |

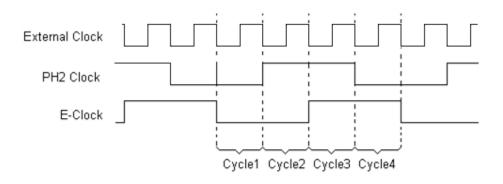

| Figure 4.4: | Internal Clock Cycles of a Bus Cycle               | 41 |

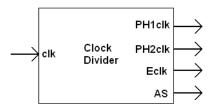

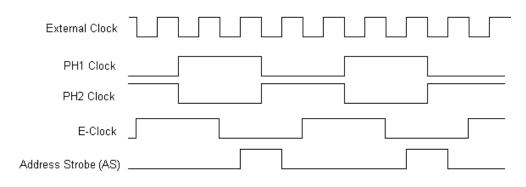

| Figure 4.5: | Clock Divider Symbol                               | 45 |

| Figure 4.6: | Internal Clock Signals of MC68HC11                 | 46 |

| Figure 4.7:  | Resulting Waveforms of Clock Divider Simulation    | 46 |

|--------------|----------------------------------------------------|----|

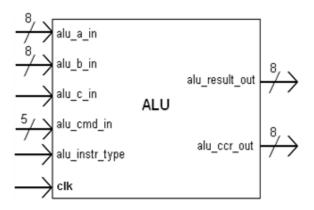

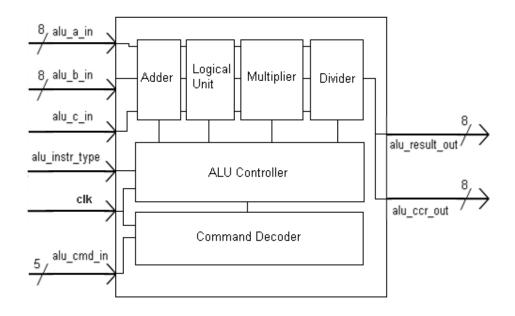

| Figure 4.8:  | Arithmetic and Logic Unit Symbol                   | 47 |

| Figure 4.9:  | ALU Block Diagram                                  | 48 |

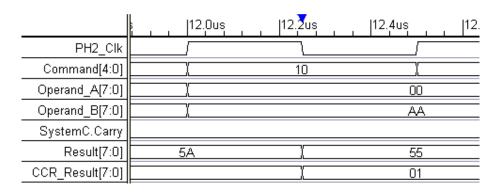

| Figure 4.10: | Arithmetic and Logic Unit Test Results             | 51 |

| Figure 4.11: | ALU Addition Test Waveforms                        | 52 |

| Figure 4.12: | ALU Increment Test Waveforms                       | 52 |

| Figure 4.13: | ALU Subtract Test Waveforms                        | 52 |

| Figure 4.14: | ALU Decrement Test Waveforms                       | 53 |

| Figure 4.15: | ALU AND Operation Test Waveforms                   | 53 |

| Figure 4.16: | ALU OR Operation Test Waveforms                    | 53 |

| Figure 4.17: | ALU XOR Operation Test Waveforms                   | 54 |

| Figure 4.18: | ALU Complement Test Waveforms                      | 54 |

| Figure 4.19: | ALU Negate Test Waveforms                          | 54 |

| Figure 4.20: | ALU Arithmetic Shift Right Test Waveforms          | 55 |

| Figure 4.21: | ALU Arithmetic / Logical Shift Left Test Waveforms | 55 |

| Figure 4.22: | ALU Logical Shift Right Test Waveforms             | 55 |

| Figure 4.23: | ALU Rotate Left Test Waveforms                     | 56 |

| Figure 4.24: | ALU Rotate Right Test Waveforms                    | 56 |

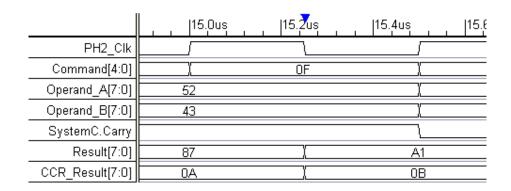

| Figure 4.25: | Register File Symbol                               | 57 |

| Figure 4.26: | Register File Test Waveforms                       | 58 |

| Figure 4.27: | Register File Test Console Outputs                 | 59 |

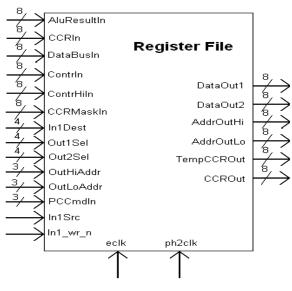

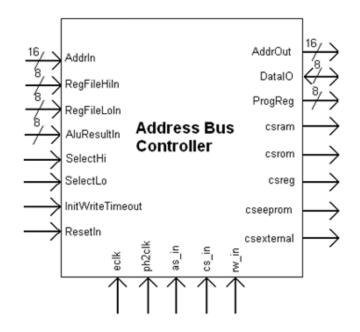

| Figure 4.28: | Address Bus Controller Symbol                      | 60 |

| Figure 4.29: | Address Bus Controller Test Results            | 61 |

|--------------|------------------------------------------------|----|

| Figure 4.30: | Console Outputs of Address Bus Controller Test | 62 |

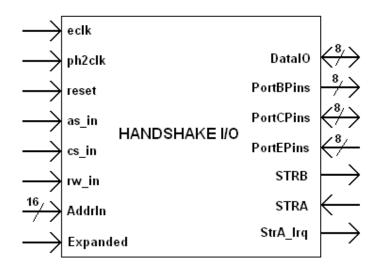

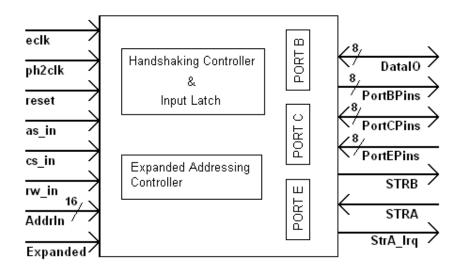

| Figure 4.31: | Handshake I/O Module Symbol                    | 63 |

| Figure 4.32: | Handshake I/O Module Block Diagram             | 64 |

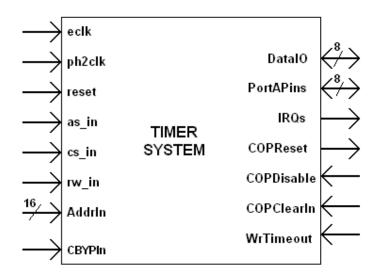

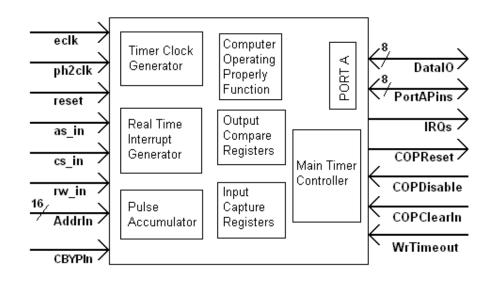

| Figure 4.33: | Timer System Symbol                            | 65 |

| Figure 4.34: | Timer System Block Diagram                     | 66 |

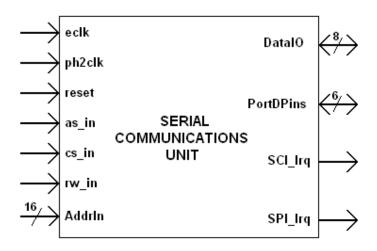

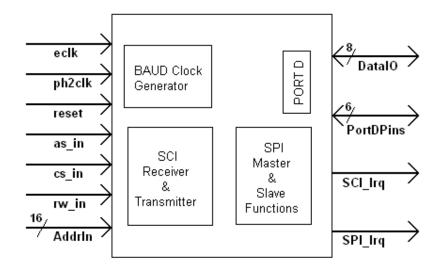

| Figure 4.35: | Serial Communications Module Symbol            | 67 |

| Figure 4.36: | Serial Communications Module Block Diagram     | 68 |

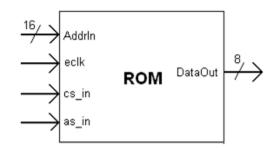

| Figure 4.37: | ROM Symbol                                     | 69 |

| Figure 4.38: | Console Output of ROM Test                     | 70 |

| Figure 4.39: | Resulting Waveforms of ROM Test                | 70 |

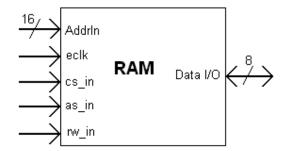

| Figure 4.40: | RAM Symbol                                     | 71 |

| Figure 4.41: | Waveforms of RAM Test Results                  | 72 |

| Figure 4.42: | RAM Test Results                               | 72 |

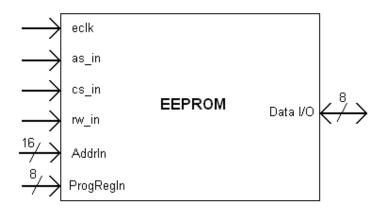

| Figure 4.43: | EEPROM Symbol                                  | 73 |

| Figure 4.44: | EEPROM Write / Read Test Results               | 74 |

| Figure 4.45: | EEPROM Clear / Read Test Results               | 75 |

| Figure 5.1:  | Visual Simulation Platform                     | 78 |

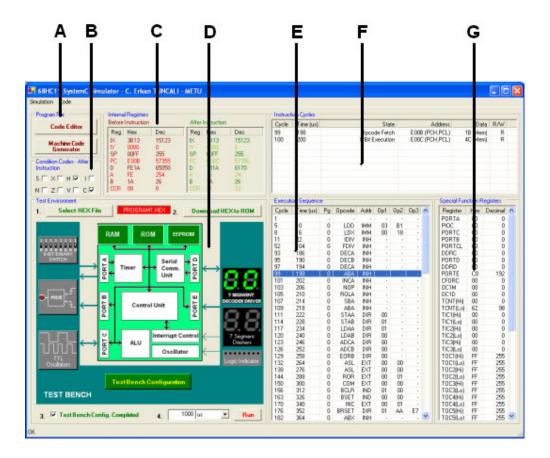

| Figure 5.2:  | Main Window of Visual Simulation Software      | 81 |

| Figure 5.3:  | 68HC11 Assembly Code Editor Window             | 82 |

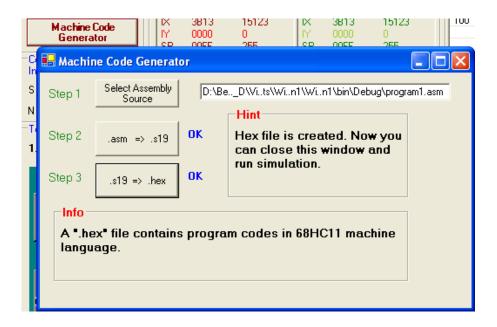

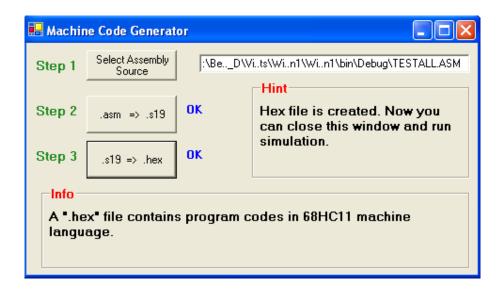

| Figure 5.4:  | Machine Code Generator Window                  | 83 |

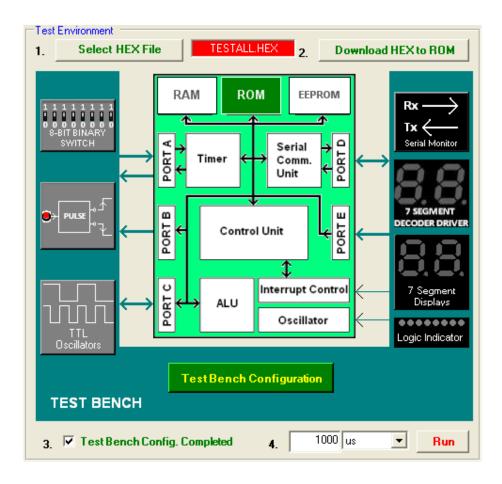

| Figure 5.5:  | Test Environment Region of Simulation Program  | 85 |

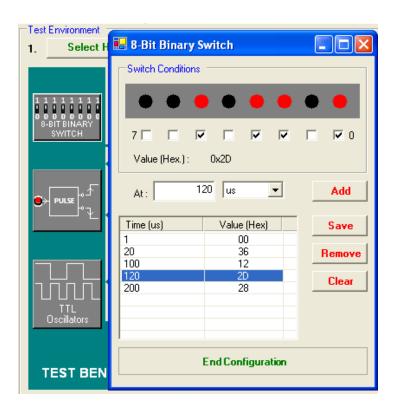

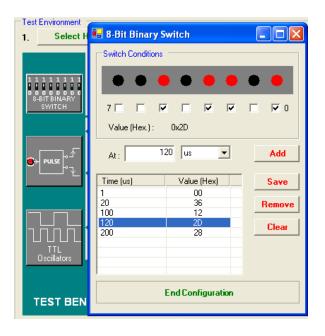

| Figure 5.6:  | 8-bit Binary Switch Configuration                      | 86  |

|--------------|--------------------------------------------------------|-----|

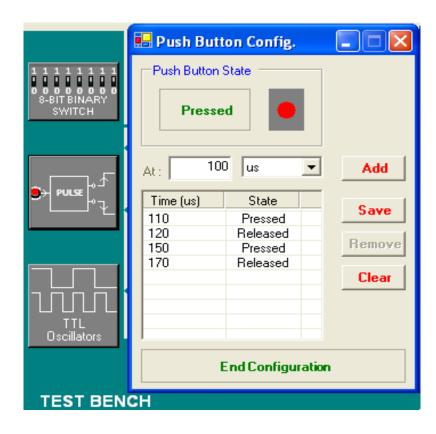

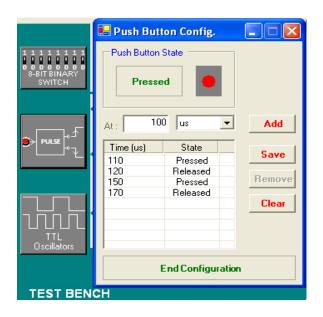

| Figure 5.7:  | Push Button Pulse Generator Configuration              | 87  |

| Figure 5.8:  | Serial Monitor Configuration                           | 88  |

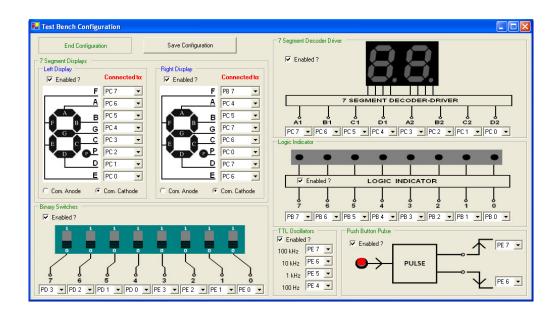

| Figure 5.9:  | Test Bench Configuration Window                        | 89  |

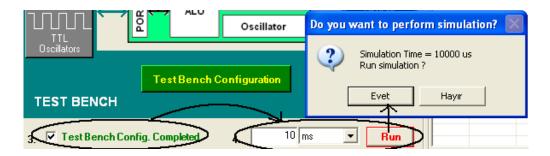

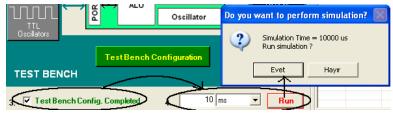

| Figure 5.10: | Running Simulation                                     | 90  |

| Figure 5.11: | Instruction and Special Function Registers Information | 91  |

| Figure 5.12: | Internal Registers Information                         | 92  |

| Figure 5.13: | RAM Content Window                                     | 92  |

| Figure 5.14: | ROM Content Window                                     | 93  |

| Figure 5.15: | EEPROM Content Window                                  | 93  |

| Figure C.1:  | Main Window of Visual Simulation Software              | 120 |

| Figure C.2:  | Code Ediitor Example                                   | 121 |

| Figure C.3:  | Code Generator Example                                 | 122 |

| Figure C.4:  | Test Environment Example                               | 123 |

| Figure C.5:  | Test Bench Port Configuration Example                  | 124 |

| Figure C.6:  | 8-bit Binary Switch Configuration                      | 125 |

| Figure C.7:  | Push Button Pulse Generator Configuration              | 125 |

| Figure C.8:  | Serial Monitor Configuration                           | 126 |

| Figure C.9:  | Running Simulation                                     | 126 |

| Figure C.10: | Simulation Results of Serial Monitor Module            | 127 |

# LIST OF TABLES

| Table 3.1: | Internal Registers of M68HC11 CPU | 23  |

|------------|-----------------------------------|-----|

| Table 3.2: | Condition Codes Register          | 24  |

| Table 3.3: | Summary of Port A Pins            | 27  |

| Table 3.4: | Summary of Port B Pins            | 28  |

| Table 3.5: | Summary of Port C Pins            | 29  |

| Table 3.6: | Summary of Port D Pins            | 30  |

| Table 4.1: | CPU States                        | 43  |

| Table 4.2: | ALU Commands and Meanings         | 49  |

| Table 4.3: | Synthesis Results of ALU Module   | 76  |

| Table A.1: | Information on Operands           | 100 |

| Table A.2: | Information on Condition Codes    | 101 |

| Table A.3: | M68HC11 Instruction Set           | 102 |

# LIST OF ABBREVIATIONS

| ALU                           | Arithmetic and Logic Unit                                                                                                          |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ASM                           | Assembly Language                                                                                                                  |  |  |

| ASIC                          | Application Specific Integrated Circuit                                                                                            |  |  |

| CCR                           | Condition Codes Register                                                                                                           |  |  |

| CISC                          | Complex Instruction Set Computer                                                                                                   |  |  |

| Co-design                     | Compound Design                                                                                                                    |  |  |

| CPU                           | Central Processing Unit                                                                                                            |  |  |

| EDA                           | Electronic Design Automation                                                                                                       |  |  |

| EDIF                          | Electronic Design Interchange Format                                                                                               |  |  |

| EEPROM                        | Electrically Erasable Programmable Read Only Memory                                                                                |  |  |

| FPGA                          | Field Programmable Gate Array                                                                                                      |  |  |

|                               | Hardware Description Language                                                                                                      |  |  |

| HDL                           | hardware beschption Language                                                                                                       |  |  |

| HDL<br>HW                     | Hardware                                                                                                                           |  |  |

|                               |                                                                                                                                    |  |  |

| HW                            | Hardware                                                                                                                           |  |  |

| HW<br>IC                      | Hardware<br>Integrated Circuit                                                                                                     |  |  |

| HW<br>IC<br>IEEE              | Hardware<br>Integrated Circuit<br>The Institute of Electrical and Electronics Engineers                                            |  |  |

| HW<br>IC<br>IEEE<br>I/O       | Hardware<br>Integrated Circuit<br>The Institute of Electrical and Electronics Engineers<br>Input / Output                          |  |  |

| HW<br>IC<br>IEEE<br>I/O<br>IP | Hardware<br>Integrated Circuit<br>The Institute of Electrical and Electronics Engineers<br>Input / Output<br>Intellectual Property |  |  |

| OSCI  | Open SystemC Initiative             |

|-------|-------------------------------------|

| PC    | Program Counter                     |

| SP    | Stack Pointer                       |

| SW    | Software                            |

| RAM   | Random Access Memory                |

| RISC  | Reduced Instruction Set Computer    |

| ROM   | Read Only Memory                    |

| RTL   | Register Transfer Level             |

| SCI   | Serial Communications Interface     |

| SPI   | Serial Peripheral Interface         |

| SoC   | System on a Chip                    |

| SRAM  | Static RAM                          |

| VCD   | Value Change Dump                   |

| VHDL  | VHSIC Hardware Description Language |

| VHSIC | Very High Speed Integrated Circuit  |

## **CHAPTER 1**

#### INTRODUCTION

Today's applications require complex electronic systems that contain multiple modules. These modules can be sub-systems, application specific integrated circuits (ASIC), microcontrollers and memory devices around central processing unit (CPU). Collecting all elements of a system on a circuit board is getting harder and more expensive as the system complexities increase. Developments in VLSI technologies allow combination of all hardware and software of systems on a single chip. Such a system is called "System On a Chip" (SoC). SoC designs allow significant reduction in size, design time and cost of a system. The need for SoC approach in system design by considering increased complexities and importance of time-to-market is presented by Kahn A. in [1].

SoC designs have both hardware and software parts. In a traditional design approach, hardware and software of a system are designed by different teams by using different tools. After hardware and software designs are completed, a prototype for system is produced where hardware and software are first brought together. Overall system tests are performed after this stage in the design flow. If design errors are discovered in these tests, hardware and software teams refine their designs and new prototypes of the system are re-manufactured. This cycle repeats itself until the system verification is successful. Prototype manufacturing is generally time consuming and expensive. This situation results in significantly increased design time and cost of the system. Compound design (co-design) approach targets to solve this problem. In this approach, both hardware and software of system are designed and verified together. Preliminary system tests can be performed before prototypes are manufactured. Co-designing and coverifying hardware and software of a system reduces the number of errors that are discovered after prototyping and the time-to-market period of a system.

Based on the requirements and the experience, system designers can use different languages and approaches for co-design purposes. Schulz S. *et al* proposed a model based specification approach for co-design [2]. SystemC, SystemVerilog, Verilog, VHDL and OpenVera are some examples of design languages. Each language has its own advantages and disadvantages over the others. For example, it is generally difficult and time consuming task to use Verilog as a high level system design language when compared to SystemC; however low abstraction level Verilog designs may yield more area and performance efficient systems. As a co-design approach, more than one language can also be used in a design flow; however interfacing subsystems that are described in different languages is difficult. Multi-language co-design approaches and interfacing problems of subsystems in these approaches are discussed by Benmohammed M. and Merniz S. in [3].

Among system design languages, ability of SystemC to model hardware and software at different abstraction levels from transaction level to register transfer level (RTL) makes it the best candidate for co-designing and co-verifying hardware and software of a system using single language. IEEE Standard SystemC language has been proposed as an ANSI standard C++ class library for system and hardware design for use by designers and architects who need to address complex systems [4]. SystemC is actually a class library which extends C++ language with new constructs for modeling hardware components. These constructs can be listed as modules, ports, processes, events, interfaces and channels. It has an event-driven simulation kernel that allows concurrency of signals. Detailed information on SystemC language, its constructs, data types and abstraction levels can be found in [4] and [5]. SystemC designs can be synthesized to RTL by using electronic design automation (EDA) tools; however not all SystemC constructs are synthesizable. A subset of SystemC language that

is suitable for synthesis is given in [6]. Celoxica Agility Compiler [7] provides a SystemC system level synthesis tool. It outputs to RTL for synthesis tools like Design Compiler and optimized Electronic Design Interchange Format (EDIF) for Altera and Xilinx FPGAs. SystemCrafter SC [8] is another software tool that synthesizes SystemC into RTL VHDL or Verilog for Xilinx FPGAs. Synthesis of SystemC transaction level and register transfer level designs are presented in [9] by Calazans N. *et al* and area comparisons are done between RTL SystemC description synthesis and RTL VHDL descriptions. Results showed that, area of hardware synthesized from SystemC is comparable with area of equivalent hardware that is synthesized from VHDL. A 4-bit microprocessor is implemented in VHDL and SystemC RTL as a case study and these implementations are compared in terms of easiness of the design, functional simulations, logic optimizations and timing analysis [10]. Their results showed that SystemC is more efficient than VHDL in terms of verification, because SystemC simulations run faster and development of test vectors are easier.

Intellectual property (IP) cores are hardware blocks that are designed using languages like VHDL, Verilog and SystemC. Implementations and verification of these cores are completed before they are delivered to customers. System designers can reduce design and verification effort by using these pre-designed and pre-verified IP cores in their system designs. IP providers deliver cores in soft or hard forms. Soft IP cores are descriptions of hardware that are ready to synthesis. Hard IP cores are already synthesized and ready to manufacture. SystemC IP cores are available and being developed all over the world. Synopsis Inc. provides SystemC models for the PowerPC processors and a broad range of peripherals as a part of its System Studio product [11]. CoWare Model Library [12] from CoWare Inc. provides a collection of SystemC IP models including ARM and MIPS processors. Open source SystemC IP cores of USB1.1 function from Usselmann R., an area improved DES coprocessor and MD5 hash algorithm from Villar J. C. are available in [13]. Jonsson B. suggests a JPEG encoder SystemC implementation in [14].

Several SystemC IP cores have been developed in Middle East Technical University (METU). Implementations of industry standard 80C51 compatible 8-bit microcontroller unit by Kesen L. [15], an 16-bit RISC based MSP430 microcontroller unit by Zengin S. [16], optimized reconfigurable Viterbi decoder by Sözen S. [17], direct digital synthesis based function generator by Kazancioglu U. [18], analog and mixed signal modeling for PIC 16F871 microcontroller unit by Mert Y. M. [19] are theses on SystemC IP models previously completed in the Electrical and Electronics Engineering Department of METU.

Companies and designers that have previously developed know-how and software for a specific microprocessor want to use this microcontroller in their new SoC designs. This situation have arisen the need for IP cores of industry standard microprocessors and microcontrollers. Using IP cores of a microcontroller give system designers the ability to use their past know-how on that microcontroller in their new SoC designs and the flexibility to remove unnecessary peripherals of microcontroller at hand and optimize its peripherals for target system or replacing old peripherals with the ones that use new standards. For example an old serial communications interface can be replaced with a modern interface such as USB 2.0 or Bluetooth. Developments in IC fabrication techniques may also allow implementation of the new microcontroller core to operate at higher frequencies than the original one.

The objective of this thesis is to make a synthesizable SystemC implementation of a microcontroller that is instruction set and timing compatible with industry standard MC68HC11 [20] [21] microcontroller with its peripheral devices and to provide a powerful simulation platform for the implemented microcontroller with a test bench and visual interface, using co-design capabilities of SystemC. With today's technology, hardware of the designed microcontroller unit can be manufactured after synthesizing the developed SystemC model to HDLs using electronic design automation tools. MC68HC11 is selected because it is widely used in several applications; it has commonly required peripherals and its well designed architecture makes it a good candidate for microprocessor architecture

4

for educational purposes. In this study, it is aimed to develop a user friendly simulator interface for configuring and running SystemC simulations of implemented system that consists of microcontroller hardware, software and test hardware. The developed simulator is also responsible for presenting simulation results in an easily understandable format. This architecture can be considered as a complete design and verification environment for MC68HC11 where microprocessor hardware and software can be tested before hardware prototypes including peripheral components are manufactured. Main difference of this simulation platform from microcontroller simulators is its usability as a synthesizable hardware model of a microcontroller.

MC68HC11 microcontroller core and its peripherals are implemented in SystemC platform using Microsoft Visual C++ 6.0. Developed core and peripheral devices are designed to mostly comply with the original ones. When compiled with appropriate flags for simulation purposes, implemented microcontroller takes simulation options and provides some information on its internal workings to outside world by using input and output files. It reads ROM and EEPROM contents from input files and provides internal register values, memory contents, some of its internal signals and operation states of microcontroller CPU in each clock cycle. Analog to digital converter module of MC68HC11 is kept out of this thesis concept because standard SystemC language does not support modeling of analog hardware.

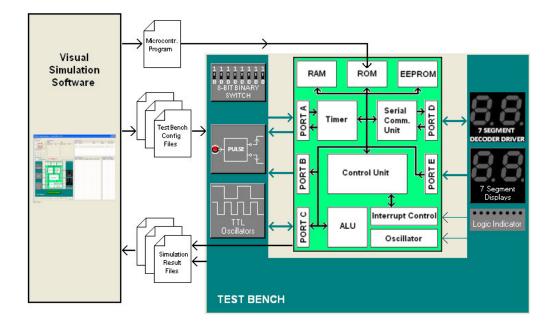

A configurable test bench which employs different input and output device modules such as serial monitor, TTL oscillators, switches and seven segment displays, is designed in a higher abstraction level than microcontroller core. This test bench communicates with a visual simulation program, which is designed as a part of overall simulation environment, using input and output files. It reads test hardware configurations and port connections from input files and writes cycle accurate simulation results to output files. Visual simulation program is developed using C# language in Microsoft .NET platform and is responsible for user

5

interaction in order to configure simulation environment and present simulation results.

In Chapter 2, using SystemC for co-design and co-verification purposes is studied. SystemC language and its capabilities are explained without much detail and how to set up a development environment for SystemC is described step by step.

Information on original MC68HC11 family of microcontroller units is given in Chapter 3. Operation and addressing modes of its central processing unit, its memory devices and peripherals are described briefly.

Chapter 4 explains the SystemC implementation of MC68HC11 microcontroller unit and its peripherals. Each SystemC module is explained separately with its structure. This chapter also presents test results of designed modules and overall microcontroller unit.

Developed simulation platform and SystemC implementation of developed test bench is explained in Chapter 5. This chapter also explains the link between SystemC implementations and visual user interface part of the developed simulation platform.

Finally in Chapter 6, conclusions of the work are presented and directions for future work are suggested. References are presented for further reading.

### **CHAPTER 2**

# USING SYSTEMC FOR HARDWARE / SOFTWARE CO-DESIGN AND CO-VERIFICATION

#### 2.1 Need for Hardware / Software Co-design of Systems

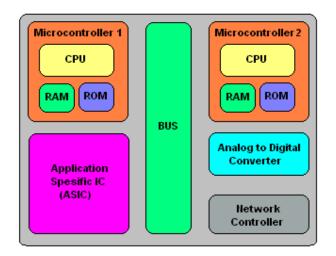

Today's SoC systems may be complex structures with multiple processors, ICs and software. They may also contain other sub-systems. Different bus interfaces connect on-chip devices and sub-systems. Figure 2.1 is presented as a typical example of SoC systems.

Figure 2.1: A Typical Example of SoC Systems.

In a traditional design flow, hardware and software parts of the systems are designed by different teams without much interaction between these parts. Design teams targets to achieve given specifications. Each part has its own design flow. After each team completes designs and a prototype of hardware is manufactured, hardware and software are brought together and overall system tests are done. Discovering design errors at this stage of overall system design flow causes large amounts of money time to companies because design flow of problematic parts should be repeated until overall system is verified. If design errors are discovered in hardware, prototyping of hardware should be done again.

Competition in the market makes a pressure on companies to reduce time-tomarket periods and costs of the systems. In order to achieve shorter design periods without any decrease in reliability of complex systems, modeling of overall architecture and integration of hardware and software parts should be done in early stages of design flow. Tests of embedded systems should be done before manufacturing hardware prototypes. Co-design technique offers designing hardware and software parts together starting from very early stages of overall system design flow. These parts are in interaction with each other during almost whole design flow and they are verified together before prototyping of hardware is done. This minimizes number of errors that are discovered after prototyping.

#### 2.2 Using SystemC for Co-design

SystemC is an open source system design language that is based on C++ language. It is actually an ANSI standard C++ class library which is developed for hardware and system design. It is developed by Open SystemC Initiative (OSCI). C++ language is inadequate for describing concurrent behavior of hardware and lacks notion of time. SystemC extends C++ library for describing hardware by providing data types for describing hardware and structure hierarchy. SystemC has a simulation kernel which has a scheduler that synchronizes execution of functions in accordance with time notion and event driven architecture of functions. Verification of a system generally takes too much time, in most cases verification period may be longer than design period. This is a handicap for reducing time to market, so simulations should be done easily and in shorter times; test benches should be developed in less time. In order to achieve these in complex systems, design tool should allow high abstraction levels as it gets harder and more time consuming to design everything in a system in register transfer level. SystemC has a great feature that it allows designing systems in high abstraction levels. This is called system level design. Using SystemC, a designer can start modeling overall architecture at a very high level of abstraction and refine model by lowering abstraction level of described parts. Using very high level abstractions and than making refinements is more difficult and sometimes impossible in other hardware description languages (HDLs). It is also possible to keep test benches at very high level without refining them in order to reduce design time without affecting reliability of tests.

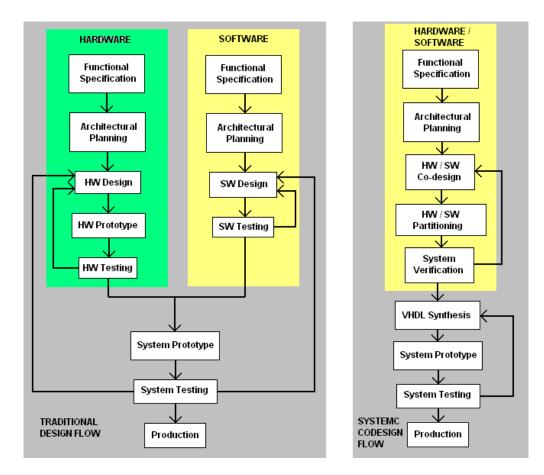

SystemC is a great platform for making hardware / software co-design of systems. Because it is a class library in C++, it inherits properties of C++ language. System designer can design both hardware and software of system using same language and making refinements on any part of the system does not affect rest of the system. Co-verification of hardware and software can also be done using SystemC during design time. Figure 2.2 shows comparison of traditional design flow with SystemC co-design flow.

Figure 2.2: Design Flow Comparison

#### 2.3 Development Environment for SystemC

In order to start making designs using SystemC and viewing simulation result waveforms, some tools are needed. First of all SystemC library source should be downloaded. Downloading documentation is also recommended. SystemC is open source and freely available at Open SystemC Initiative web site *"www.systemc.org"*. During this thesis work, SystemC library version 2.1.v.1 is used. After downloading SystemC library source, it should be compiled to generate a library file for design environment. Any C++ compiler can be used to generate library file. Microsoft XP is used as operating system and Microsoft Visual C++ 6.0 is used for C++ compilation in this thesis work. Steps for compiling source of SystemC library in Microsoft Visual C++ 6.0 are presented below. SystemC documentation can be used as a guideline for library creation process for different development environments.

SystemC library compilation steps:

- 1. Downloaded source files come in an archive file. This archive should be extracted to any folder using a suitable archive manager program.

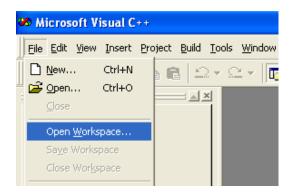

- In Microsoft Visual C++, "Open Workspace..." menu item under "File" menu should be clicked and "systemc.dsw" file should be selected by browsing into "msvc60\SystemC" directory which is under the directory where library source files are extracted.

Figure 2.3: "Open Workspace" Menu Item in Microsoft Visual C++

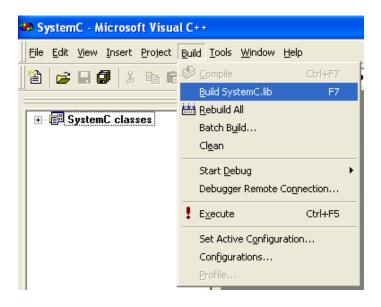

Workspace file is adjusted for compilation of SystemC library in Microsoft Visual C++. Selecting "Build systemc.lib" under "Build" menu is enough for compilation of the library.

Figure 2.4: Building SystemC Library

For creating a SystemC project, a new empty Win32 console application should be created first. After creating a new project, some adjustments should be done on this project options for SystemC compilation. Below are steps of creating a SystemC design in Microsoft Visual C++. Compiler documentation can be referred for better understanding.

SystemC project creation steps in Microsoft Visual C++:

- A new, empty C++ project is created by using "New" menu item under "File" menu and selecting "Win32 Console Application" option.

- "Enable Run-Time Type Information (RTTI)" checkbox should be checked by selecting "C++ Language" category in "C/C++" tab under "Settings" menu item of "Project" menu. This is shown in Figure 2.5.

| Project Settings          | ? 🔀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Settings For: Win32 Debug | General       Debug       C/C++       Link       Resourc       Image: Construction         Category:       C++ Language       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: C++       Image: |

|                           | OKCancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Figure 2.5: Enabling Run-Time Type Information

For using SystemC data types and functions, SystemC library should be used in link step. Under "Projects" menu and "Settings" menu item, "Link" tab should be selected and "systemc.lib" should be added to the "Object / library modules" list. This is presented in Figure 2.6 below.

Figure 2.6: Including SystemC Library to Library List

4. Include file and library directory search paths should be added to project. For doing this, "Settings" menu item is selected under "Project" menu. Under "C/C++" tab, "Preprocessor" category is selected and path of "src" directory which is in extracted SystemC library directory is entered in text field into area labeled "Additional include directories". Path to SystemC library which is under "msvc60\systemc\debug" directory in extracted SystemC library directory is entered in "Additional library directory in extracted SystemC library directory is entered in "Additional library directory in extracted SystemC library directory is entered in "Additional library path" text box under "Input" category in "Link" tab.

Project settings are completed for SystemC compilation. After adding source files to created project and developing SystemC model, "Build" menu can be used for generating executable program file of developed model.

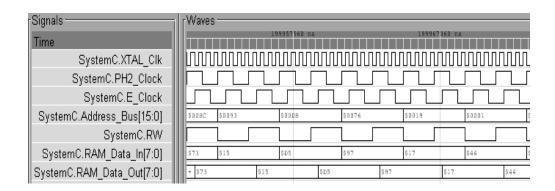

If SystemC code is written appropriately for value change dump (.vcd) file generation, which is achieved by using "sc\_trace" method of SystemC library, executable file will generate a ".vcd" file (also called trace file) that contains simulation waveforms of selected signals. There are different programs that can be used to view these trace files. In this thesis "GTKWave" application is used for this purpose. In order to see waveforms in GTKWave, "Search -> Signal Search Tree" menu should be accessed and signals that are wanted to be shown on screen should be selected and inserted. Figure 2.7 shows an example screenshot from GTKWave for inserting signals.

Figure 2.7: Inserting Signals in GTKWave.

### **CHAPTER 3**

### M68HC11 FAMILY OF MICROCONTROLLER UNITS

MC68HC11 microcontroller is briefly explained in this chapter with its core and peripheral functions. Reader can refer to M68HC11 E Series datasheet [20] and M68HC11 reference manual [21] for more detail.

#### 3.1 General Description

M68HC11 is a family of 8-bit general purpose microcontroller units. Members of this family differ from each other with small differences in their components. In this thesis a SystemC design best matches to this microcontroller unit family members is done. MC68HC11E9 microcontroller unit which is a M68HC11 family member is chosen as a model. MC68HC11E9 is chosen because it has most of the peripherals available in the family, it is used in Motorola Semiconductors Evaluation Board (EVBU) which is used widely for educational purposes and vast amount of information on this model is available.

There are different packaging options for different members of M68HC11 family of microcontroller unit. For MC68HC11E9 52-pin plastic leaded chip carrier (PLCC), 52-pin windowed ceramic-leaded chip carrier (CLCC), 64-pin quad flat pack (QFP), 52-pin thin quad flat pack (TQFP) and 56 pin shrink dual in-line package (SDIP) options are available. Most of the pins serve at least two different functions. Pin assignments for 52-pin PLCC package option of MC68HC11E9 are presented in Figure 3.1.

Figure 3.1: MC68HC11E9 Pin Assignments

MC68HC11E9 can operate at external clock frequencies up to 8 MHz which generates up to 2 MHz of internal bus clock. It has peripheral functions including an 8-channel A/D (analog-to-digital) converter which has 8-bits of resolution, an asynchronous serial communications interface (SCI), a synchronous serial peripheral interface (SPI), a 16-bit, free running main timer system with three input-capture lines, five output compare lines and a real-time interrupt function. An 8-bit pulse accumulator subsystem that can count external events or measure externally applied signal periods is also included in MC68HC11E9. On-chip memory systems of MC68HC11E9 include 8 Kbytes of read-only memory (ROM), 512 bytes of electrically erasable programmable ROM (EEPROM) and 256 bytes of random access memory (RAM). These peripherals and on-chip memory can be seen on block diagram of MC68HC11E9 in Figure 3.2

Figure 3.2: Block Diagram of MC68HC11E9

# 3.2 Operation Modes of MC68HC11

MC68HC11 microcontroller unit has two main operation modes. These are:

- Single-chip operation mode

- Expanded operation mode

Each of these main operation modes also has two variations. These variations are called normal and special variations. All operation modes are listed below:

- Normal single-chip operation mode

- Special bootstrap mode (special variation of single-chip mode)

- Normal expanded operation mode

- Special test mode (special variation of expanded operation mode)

In normal single-chip mode of operation everything that will be accessed using address and data buses is assumed to be contained in microcontroller chip. There are no external memory elements or peripherals in this mode of operation.

Normal variation of expanded operation mode is used for accessing external memory and/or peripherals. In this mode of operation, address/data bus is multiplexed and available on port B and port C pins. Normal expanded mode of operation has two additional control pins.

Special bootstrap mode is used for downloading programs into on-chip RAM at startup using asynchronous serial communications interface (SCI). Special test mode generally used for factory testing of microcontroller.

# 3.3 On-Chip Memory Systems

MC68HC11 microcontroller unit includes 512 bytes of random access memory (RAM), 12 Kbytes of program (user) read-only memory (ROM), 192 bytes of bootloader ROM and 512 bytes of electrically erasable programmable ROM (EEPROM). Other members of M68HC11 family may have different sizes of RAM, ROM and EEPROM memories. ROM or EEPROM memories are not included or disabled in some variations of microcontroller units in M68HC11 family. Memory map of MC68HC11E9 is presented in Figure 3.3.

Figure 3.3: Memory Map of MC68HC11E9

#### 3.3.1 Read-Only Memory (ROM)

There are two read only memories (ROMs) on MC68HC11 microcontrollers. One of them is called program ROM or user ROM and the other one is bootloader ROM.

As its name implies, program ROM contains instructions of user's program. Program ROM is not writable or changeable by user after fabrication, so instructions of program are stored into this memory when the microcontroller unit is manufactured. Program ROM occupies 12 Kbytes in 64 Kbytes memory space of microcontroller unit. User may disable on-chip ROM if not needed. If ROM is disabled it does not occupy area in memory space anymore.

Other read-only memory included in MC68HC11 microcontrollers is 192 byte bootloader ROM. This memory unit is used for loading bootloader program in special bootstrap mode. In normal operation modes, bootloader ROM is disabled and does not occupy any area in memory space of microcontroller.

#### 3.3.2 Random-Access Memory (RAM)

Random access memory can be thought as a temporary storage space during runtime. User's program accesses to this memory during execution and uses this memory space for storing and reading variables for making operations on them.

RAM occupies first 512 bytes of memory space normally, but it can be mapped to beginning of other blocks of memory space in first 64 CPU cycles of microcontroller operation.

#### 3.3.3 Electrically Erasable Programmable ROM (EEPROM)

EEPROM allows user to store and change programs when needed after manufacturing of microcontroller unit is completed. With the help of this memory unit, user programs may be updated at any time.

MC68HC11E9 has 512 bytes of on-chip EEPROM. In MC68HC11 microcontrollers in addition to this EEPROM unit, there is another EEPROM byte which is used for controlling some basic features. This EEPROM byte is named as "CONFIG" register.

EEPROM in the MC68HC11E9 is fixed at locations \$B600-\$B7FF. Reads from EEPROM memory can be done by a read operation from address of location to be read. Writes to EEPROM is controlled by EEPROM programming register (PPROG). For writing to a location, first EEPROM programming voltage should be enabled using EEPGM bit in PPROG register, then write operation should be performed to the location and finally EEPROM programming voltage should be disabled again. There are different ways to erase EEPROM locations. These are; "byte erase", in which EEPROM locations are erased one by one; "row erase", in which EEPROM locations are erased in rows and finally "bulk erase" in which all bytes of EEPROM are erased at once. These methods are not applicable to erasure of CONFIG register.

#### 3.4 Central Processing Unit (CPU)

MC68HC11 microcontrollers utilize M68HC11 central processing unit (CPU). CPU is responsible for executing software instructions in their programmed sequence. There are 235 different operation codes (opcodes) in M68HC11 instruction set, using page-select prebytes before opcodes, some new instructions are specified and a total number of 310 instructions are reached.

The M68HC11 CPU accesses all input/output, peripheral and memory locations as any location in memory space. This technique of access is called memory-mapped I/O.

M68HC11 CPU contains two accumulators named accumulator A and B. Accumulators A and B form double accumulator D together. There are two index registers (IX and IY) in CPU which are generally used for calculating indexed addresses. Stack pointer (SP), which is a CPU register, always points to next free location of stack area. Program Counter register (PC), as its name implies, holds address of next program instruction. Condition code register (CCR) holds status indicator flags that indicate status of CPU after last instruction is executed. Table 3.1 shows internal registers of M68HC11 central processing unit.

| Register                      | Explanation                                                                         |

|-------------------------------|-------------------------------------------------------------------------------------|

| Accumulator A                 | 8 bit accumulator                                                                   |

| Accumulator B                 | 8 bit accumulator                                                                   |

| Double Accumulator D          | Concatenation of accumulators A and B (A:B)                                         |

| Index Register IX             | 16 bit index register                                                               |

| Index Register IY             | 16 bit index register                                                               |

| Stack Pointer (SP)            | 16 bit stack location pointer                                                       |

| Program Counter (PC)          | 16 bit program instruction pointer                                                  |

| Condition Code Register (CCR) | 8 bit register with status indicators, interrupt masking bits and STOP disable bit. |

Table 3.1: Internal Registers of M68HC11 CPU

Five status indicators in condition code register give some information on execution and results of instructions. Two interrupt masking bits are used for masking global interrupts and interrupts generated from  $\overline{\text{XIRQ}}$  pin. STOP disable bit is used for avoiding STOP instruction to stop microcontroller operation. Table 3.2 summarizes meanings of flags in condition code register.

| Table 3.2: | Condition Co | odes Register |

|------------|--------------|---------------|

|------------|--------------|---------------|

| CCR Bit              | Bit<br>Location | Meaning                                                                   |

|----------------------|-----------------|---------------------------------------------------------------------------|

| Carry (C)            | 0               | A carry out or borrow has occurred as a result of operation.              |

| Overflow (V)         | 1               | Indicates a two's complement overflow condition as a result of operation. |

| Zero (Z)             | 2               | Informs whether the result of operation is zero or not.                   |

| Negative (N)         | 3               | Indicates that result of the operation is negative.                       |

| I Interrupt Mask (I) | 4               | Disables all maskable interrupts.                                         |

| Half Carry (H)       | 5               | Set if carry from bit 3 has occurred.                                     |

| X Interrupt Mask (X) | 6               | Disables <i>XIRQ</i> pin interrupt.                                       |

| STOP Disable (S)     | 7               | Disables STOP instruction.                                                |

#### 3.5 Addressing Modes

M68HC11 uses six different ways for accessing memory. These are called "addressing modes". Addressing modes are techniques for calculating address information for memory access. Different modes of addressing in M68HC11 are immediate, extended, direct, indexed, inherent and relative addressing modes. These are studied in detail in following subsections.

# 3.5.1 Immediate Addressing Mode

In immediate addressing mode there is no need to calculate an effective address to access data. Data needed is contained in bytes following opcode. Number of data bytes is specific to opcode.

#### 3.5.2 Extended Addressing Mode

In the extended addressing mode, two bytes following the opcode are effective address of the data needed. No other calculations are needed; reading these two bytes is enough for knowing effective address.

#### 3.5.3 Direct Addressing Mode

Direct addressing mode which is also called "zero page addressing mode" is used for accessing only to first 256 locations of memory space. High order byte of effective address is zero and low order byte of the effective address is contained in byte following the opcode.

#### 3.5.4 Indexed Addressing Mode

In the indexed addressing mode, an offset value is contained in the byte following the opcode. Effective address is calculated by adding this offset value to one of the index registers. Information on which index register will be used for address calculation is specific to opcode.

#### 3.5.5 Inherent Addressing Mode

In the inherent addressing mode no address information is needed because actually no addressing is done. Information on operands is available in opcode.

#### 3.5.6 Relative Addressing Mode

Relative addressing mode is used for accessing a location within a range of  $\pm 128$  relative to program counter. Offset to program counter is available in the byte following the opcode. This offset value is actually a signed byte. Relative addressing mode is only used for branching program execution purposes.

# 3.6 Parallel Input / Output (I/O)

The MC68HC11E9 has five input / output (I/O) ports and 40 I/O pins that are shared between these ports. All I/O pins also have alternative functions. These alternative functions are used by peripheral systems of microcontroller unit. Input / output ports are named port A to port E. Number of pins on these ports may not be equal to each other. Some of these pins are fixed-direction input or fixed-direction output pins and some of them are bidirectional pins.

#### 3.6.1 Data Ports

Port A is an 8-bit port with three fixed-direction input pins, four fixed-direction output pins and one bidirectional pin. Port A pin 7 can be configured as input or output port using DDRA7 bit in PACTL register. Port A pins can be used as general purpose input/output pins and they also have alternative functions. Table 3.3 summarizes alternative functions of port A pins.

| Pin | GPIO feature           | Alternative function(s)                  |

|-----|------------------------|------------------------------------------|

| PA0 | Fixed-direction input  | Input capture                            |

| PA1 | Fixed-direction input  | Input capture                            |

| PA2 | Fixed-direction input  | Input capture                            |

| PA3 | Fixed-direction output | Output compare                           |

| PA4 | Fixed-direction output | Output compare                           |

| PA5 | Fixed-direction output | Output compare                           |

| PA6 | Fixed-direction output | Output compare                           |

| PA7 | Bidirectional          | Pulse accumulator input / Output compare |

Table 3.3: Summary of Port A Pins

Port B and port C actually function together with STRA and STRB pins of microcontroller unit. These ports and pins are all together form handshake I/O

subsystem in single-chip mode and multiplexed address/data bus in expanded mode. Information on handshake I/O subsystem can be found in section 3.6.2.

Port B is an 8-bit port which has all of its pins as fixed-direction outputs. As these pins can be used for general purpose output, they also have alternative functions in expanded operation mode. Port B is a part of handshake I/O subsystem. Handshake I/O properties of port B is summarized in section 3.6.2. In expanded operation mode, port B serves as high order byte of address information. Table 3.4 presents functions of port B pins.

| Pin | GPIO feature           | Alternative function(s)  |

|-----|------------------------|--------------------------|

| PB0 | Fixed-direction output | Address bus bit 8 (A8)   |

| PB1 | Fixed-direction output | Address bus bit 9 (A9)   |

| PB2 | Fixed-direction output | Address bus bit 10 (A10) |

| PB3 | Fixed-direction output | Address bus bit 11 (A11) |

| PB4 | Fixed-direction output | Address bus bit 12 (A12) |

| PB5 | Fixed-direction output | Address bus bit 13 (A13) |

| PB6 | Fixed-direction output | Address bus bit 14 (A14) |

| PB7 | Fixed-direction output | Address bus bit 15 (A15) |

Table 3.4: Summary of Port B Pins

Port C is an 8-bit port. All pins of port C can be used as bidirectional general purpose input/output pins. Port C is a part of handshake I/O subsystem. In expanded mode of microcontroller operation, this port is used for multiplexed address / data bus. Table 3.5 lists functions of port C pins.

| Pin | GPIO feature  | Alternative function(s)        |

|-----|---------------|--------------------------------|

| PC0 | Bidirectional | Address / data bus bit 0 (AD0) |

| PC1 | Bidirectional | Address / data bus bit 1 (AD1) |

| PC2 | Bidirectional | Address / data bus bit 2 (AD2) |

| PC3 | Bidirectional | Address / data bus bit 3 (AD3) |

| PC4 | Bidirectional | Address / data bus bit 4 (AD4) |

| PC5 | Bidirectional | Address / data bus bit 5 (AD5) |

| PC6 | Bidirectional | Address / data bus bit 6 (AD6) |

| PC7 | Bidirectional | Address / data bus bit 7 (AD7) |

Table 3.5: Summary of Port C Pins

Port D is a 6-bit bidirectional parallel data port. Two of port D pins alternatively function as part of asynchronous communications interface (SCI) subsystem. Other four pins alternatively function as a part of synchronous serial peripheral interface (SPI) subsystem. All six pins of port D can also be used for general purpose input/output functions. Summary on port D functions can be found in Table 3.6.

| Table 3.6: | Summary of Port D Pins |

|------------|------------------------|

|------------|------------------------|

| Pin | GPIO feature  | Alternative function(s)          |

|-----|---------------|----------------------------------|

| PD0 | Bidirectional | SCI Receive data (RxD)           |

| PD1 | Bidirectional | SCI Transmit data (TxD)          |

| PD2 | Bidirectional | SPI Master in / slave out (MISO) |

| PD3 | Bidirectional | SPI Master out / slave in (MOSI) |

| PD4 | Bidirectional | SPI Master clock out (SCK)       |

| PD5 | Bidirectional | SPI Slave select (SS)            |

Port E is an 8-bit fixed-direction input port. Pins of port E alternatively function as analog-to-digital (A/D) converter channel inputs.

#### 3.6.2 Handshake I/O Subsystem

Handshake I/O subsystem is used for sending and receiving data to external devices in a more guaranteed way than normal parallel I/O. Ports B and C, STRA input pin, STRB output pin are parts of this subsystem. Each device or only one device that takes place in data transfer informs other side when it reads and/or writes data to port. Operation mode of handshake I/O subsystem determines handshaking rules. Operation modes are called simple strobe mode, full-input handshake mode and full-output handshake mode.

In simple strobe mode, port B is used as a simple output port which works together with STRB strobe output and port C is used as a simple latching input together

with STRA strobe input. Input and output work independent of each other. In simple strobe mode of handshake operation, a strobe signal is generated at STRB pin whenever a data is written to port B. Data is read from port C and latched when an active edge is encountered at STRA input.

Only port C, STRA and STRB pins are used in full-input handshake mode. In this mode, a selected edge at STRA input causes data on port C to be latched into a register and negation of STRB output. When the latched data is read in microcontroller, STRB output is asserted again to indicate that data reception is complete. In this mode, external system knows when to write data on port C using STRB information. As a summary, data sending system informs receiving system when it writes data to port and data receiving system informs data sending system when it reads data from port.

In full-output handshake mode, external system is informed via STRB pin when a data is written on port C and ready signal is read from STRA pin which indicates that external system has read data from port. Full-output and full-input handshake modes can be though as two different ends of data receiving and sending systems. Full-output handshake mode has a variation named three-state full-output handshake mode. In this mode, port C pins becomes driven outputs when STRA goes to its active level.

### 3.7 Synchronous Serial Peripheral Interface (SPI)

Synchronous serial peripheral interface (SPI) can be used for communicating other microcontroller units or peripheral devices. SPI system can be configured as master or slave. If it is configured as master, communication speed can be as high as 1 Mbps and if it is configured as slave communication speed can be as high as 2 Mbps.

In an SPI transfer, a clock, which is generated by master device, synchronizes shifting and sampling jobs. Shifting out of data and sampling of incoming bit occurs

at opposite edges of clock line, so reception and transmission occurs simultaneously. Any slave device which is not selected via slave select input does not read or write data from / to SPI bus.

In an SPI system only one master bus should be in communication network at a moment. When SPI system is configured as a master and another device becomes bus master, this situation is detected and SPI output drivers are disabled to avoid harms. Error detection system which detects this condition is named "multiple-master fault detector". There is another error detector in SPI which is called "write-collision detector". This system detects and avoids a write attempt to serial shift register while a transfer is in progress.

There are two different transfer formats of SPI system and these transfer formats have two different clock polarity variations. Figures 3.4 and 3.5 which are taken from *"MC68HC11 Reference Manual"* presents timing diagrams of CPHA equals zero and CPHA equals one SPI transfer formats respectively.

Figure 3.4: CPHA Equals Zero SPI Transfer Format

As seen in Figure 3.4, in CPHA equals zero transfer format, transfer is started when  $\overline{SS}$  line goes to low. When CPHA equals one transfer format is selected, transfer is started with first selected clock edge.  $\overline{SS}$  line should be low for both transfer formats.

Figure 3.5: CPHA Equals One SPI Transfer Format

#### 3.8 Asynchronous Serial Communications Interface (SCI)

Asynchronous serial communications interface (SCI) used in MC68HC11 microcontrollers is full-duplex and uses one start bit, eight or nine data bits, one stop bit none return to zero (NRZ) transfer format. SCI system has a transmitter and a receiver part. Although they use same transfer formats and same baud rates, transmitter and receiver parts of SCI system operate independent from each other. Baud rates are generated using PH2-clock of microcontroller unit.

Transmitter of SCI is double-buffered so a character can be written to transmit buffer while transmission of a character is in progress. Break and idle characters can be queued for transmission. Transmitter can generate "transmit complete" interrupt when it finishes sending all data in its queue or "transmitter data register empty" interrupt when transmit data register is available for new character.

Receiver of SCI system is also double-buffered, so software has some time to read received character before next character is received. Receiver can go to sleep mode and wake-up when selected event occurs on line. Wake-up can be initiated by an idle-line or address-mark detection in received data. SCI receiver of MC68HC11 has an advanced noise detection and correction technique. This technique is called "data sampling technique". Receiver samples line data with a clock frequency of 16 times the baud rate and uses these samples to decide logic level of received bit. A start bit is recognized if a zero is sampled after three ones and at least two of third fifth and seventh samples are zeroes. Reception is synchronized to start bit in this way. Other bits are recognized by using eighth ninth and tenth samples taken. If at least one of these samples does not agree with others, noise flag is set. Received bit is decided by using majority of samples. Generally detection would be correct even there is noise on line.

Figure 3.6: Start Bit Reception

Figure 3.6 shows an example of start bit detection with some noise on line. Although in this example start bit is received correctly, there may be some shifts in locations of perceived and actual start bits due to amount of noise on line. If these shifts are in an acceptable range, data sampling is expected to correctly receive rest of incoming character.

#### 3.9 Main Timer and Real Time Interrupt

Main timer system has a free running 16-bit counter. Counting frequency of this counter can be programmed by user. Main time system includes three input capture and four output compare subsystems, real time interrupt logic and computer operating properly (COP) watchdog timer.

Input capture function records value of free running counter when a selected edge is detected on corresponding input line. Input capture functions can generate interrupt requests. This feature of input capture functions can be used for measuring period or length of a signal on input pin.

Output compare functions generate an output when selected time has been reached. In order to do this, an output compare register is loaded with 16-bit value and when free running counter reaches to this value, a signal is outputted to indicate the condition. Output compare functions can also generate interrupts when selected count is reached by free running counter.

Computer operation properly (COP) watchdog timer function is used for resetting microcontroller if a software error occurs. COP timer counts up with user selected frequency and when it overflows microcontroller reset signal is generated automatically. Software which is running properly should touch to COP timer and clear it if COP is enabled. COP overflow means that software is not running properly so it could not clear COP timer, so microcontroller should be reset to correct this situation with a fresh startup.

35

Real time interrupt logic generates hardware interrupts with a user defined period. RTI can be used for sharing microcontroller time between different tasks for multitasking.

# 3.10 Pulse Accumulator

Pulse accumulator is actually an 8-bit counter that is used for counting selected events or gated time accumulation. It can generate interrupt requests at every event detected or when overflow occurs in 8-bit counter.

In event counting mode, pulse accumulator counts number of edges signal on PAI input. It can be configured to count positive or negative edges.

In gated time accumulation mode, 8 bit counter is incremented at every 64 E-clock cycles of microcontroller. The name "gated" comes from the feature that, counting operation is gated to PAI input. That means counting stops if PAI input is not its selected level. This feature can be used to measure durations of events.

# **CHAPTER 4**

# DESIGN OF MC68HC11 MICROCONTROLLER MODEL USING SYSTEMC

The object oriented nature of SystemC allows parts of a system to be designed as separate modules. These modules can also be divided into sub modules. This ability of SystemC allows unnecessary modules to be extracted from the whole design, adding new modules to the design and using different abstraction levels within different modules. Opportunity to use different abstraction levels for different modules makes it possible to refine modules of a system independently without affecting rest of the design.

In this thesis, the MC68HC11 microcontroller unit is divided into sub modules and each sub module is implemented in SystemC as a part of overall microcontroller system. These sub modules are, address bus controller, clock generator, arithmetic and logic unit, controller unit, handshake I/O sub-system, timer system, RAM, ROM, register file and serial communications modules. SystemC modules have been shaped according to design complexity, similarities and common requirements of peripherals in microcontroller unit. Modules that constitute microcontroller core are tested and verified before they are brought together. Although original MC68HC11E9 model has an analog to digital converter subsystem; SystemC design made in this thesis does not contain analog to digital converter module because standard SystemC library does not have data types for modeling analog hardware.

SystemC implementation of MC68HC11 microcontroller unit is explained in this chapter. Internal structure of designed microcontroller is given. Modules that construct microcontroller are explained and their test results are presented.

# 4.1 MC68HC11 SystemC Model Internal Structure

Inside the MC68HC11 microcontroller model, all modules are interconnected to each other by internal signals. Correct timing of these internal signals is very important for correct operation of overall microcontroller model. Internal signals may be divided into four categories mainly. These are internal clock signals that synchronize modules with each other, control bus signals that are used for maintaining correct operation of modules, data bus signals that carry data and address bus signals that carry address information for memory modules. Internal structure of MC68HC11 SystemC model and interconnections between modules are presented in Figure 4.1 without much detail.